6.C.2 ESTRUCTURA DE UN CCD

El Silicio es la clave del tema. Tiene un salto energético de 1.14 eV entre las bandas de valencia y de conducción. Los fotones que llegan pueden interactuar con los átomos de silicio y excitar los electrones de valencia hasta ubicarlos en la banda de conducción creando así pares (electrón-agujero). Estos pares se mueven libremente y se difunden en la estructura del silicio. La vida media de estos pares es de 100 seg. Después de este tiempo el par se recombina. Los fotones con energías de 1.1 eV a 5 eV generan un par e-h por cada fotón mientras que los fotones con energías > 5 eV producen pares múltiples. Por ejemplo un fotón de Lyman (1216 A o 10 eV) genera en promedio tres pares. El efecto fotoeléctrico útil en el silicio se extiende desde energías de 1.1 eV a 10 eV. Estas energías cubren el cercano infrarrojo, el ultravioleta, el ultravioleta lejano y los rayos X suaves. El corte para el infrarrojo ocurre debido a que el fotón no tiene energía para elevar al electrón desde la banda de valencia a la banda de conducción. Estos fotones no son absorbidos, el silicio es transparente a los mismos. Para energías >10 eV la probabilidad de interacción del fotón es muy pequeña y por lo tanto el Silicio también es transparente a esa radiación.

El capacitor MIS (metal insulator semiconductor) es el bloque constructivo crucial del CCD y puede ser fabricado sobre silicio epitelial de tipo p que significa que tiene agregadas "impurezas" que generalmente consisten en pizcas de Boro.

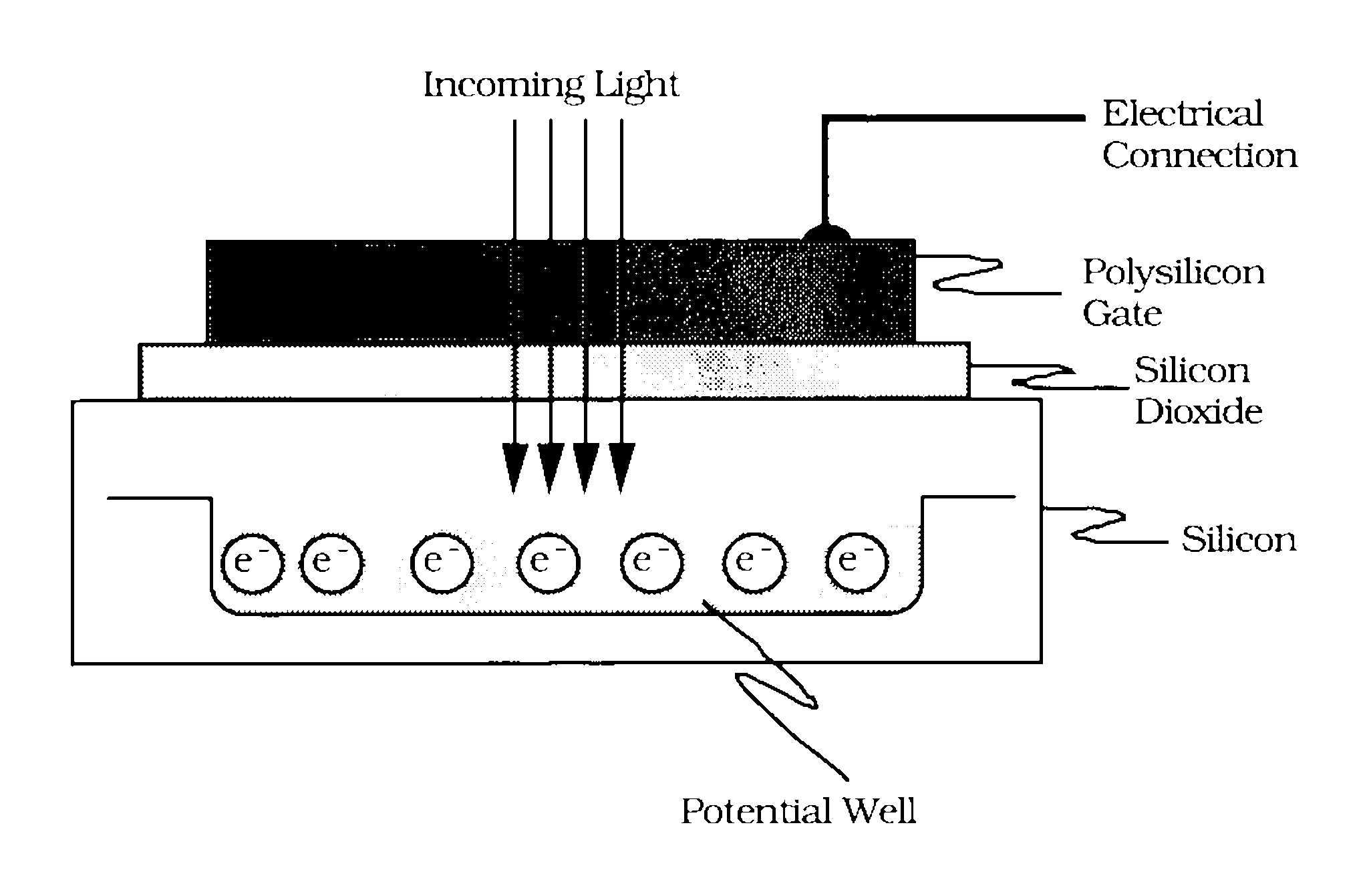

Los CCD se construyen a partir de obleas de cristales de silicio del orden de 10 cm de diámetro y medio milímetro de espesor. Este silicio es como hemos dicho del tipo p. Térmicamente se genera una capa aislante muy delgada de dióxido de silicio en la superficie del silicio. Luego se evapora sobre el aislante una capa metálica muy fina. La Figura 5-12 muestra el esquema típico de un capacitor MIS.

Figura 5-12: Esquema típico de un capacitor MIS

Evidentemente para medir la carga electrónica almacenada en el capacitor tal como describimos más arriba y que es producida por los fotones incidentes es necesario primero guardar esa carga en algún lado. De allí surge el concepto del "valle de potencial" . Este concepto puede explicarse así:

Se aplica un potencial positivo a la capa metálica delgada o compuerta ("gate") como se la denomina normalmente y entonces los agujeros, positivos pues denotan falta del electrón negativo, son forzados alejarse creando una región de vaciamiento ("depletion") sin cargas móviles

Figura 5.13: Estructura de un capacitor MOS.}

Supongamos ahora que el chip CCD es iluminado sobre su cara metálica como muestra la Figura 5-12. La luz pasa a través de la capa metálica transparente. Una parte de la luz incidente es absorbida generando pares electrón-agujero. El campo eléctrico generado por la aplicación de un voltaje positivo en la capa metálica actúa sobre las nuevas cargas generadas, repeliendo a los agujeros hacia el interior del material semiconductor (silicio).

Los electrones por el contrario viajarán hacia las compuerta o gates y lo harán hasta alcanzar la frontera divisoria entre el silicio y el dióxido de silicio. Los electrones permanecen allí. Estos chips denominados gruesos ("thick"), son muy sensibles al infrarrojo pero no al ultravioleta. En el pico máximo de eficiencia la sensibilidad puede llegar al 50%. En el ultravioleta no son sensibles para longitudes de onda menores que 4.500 A.

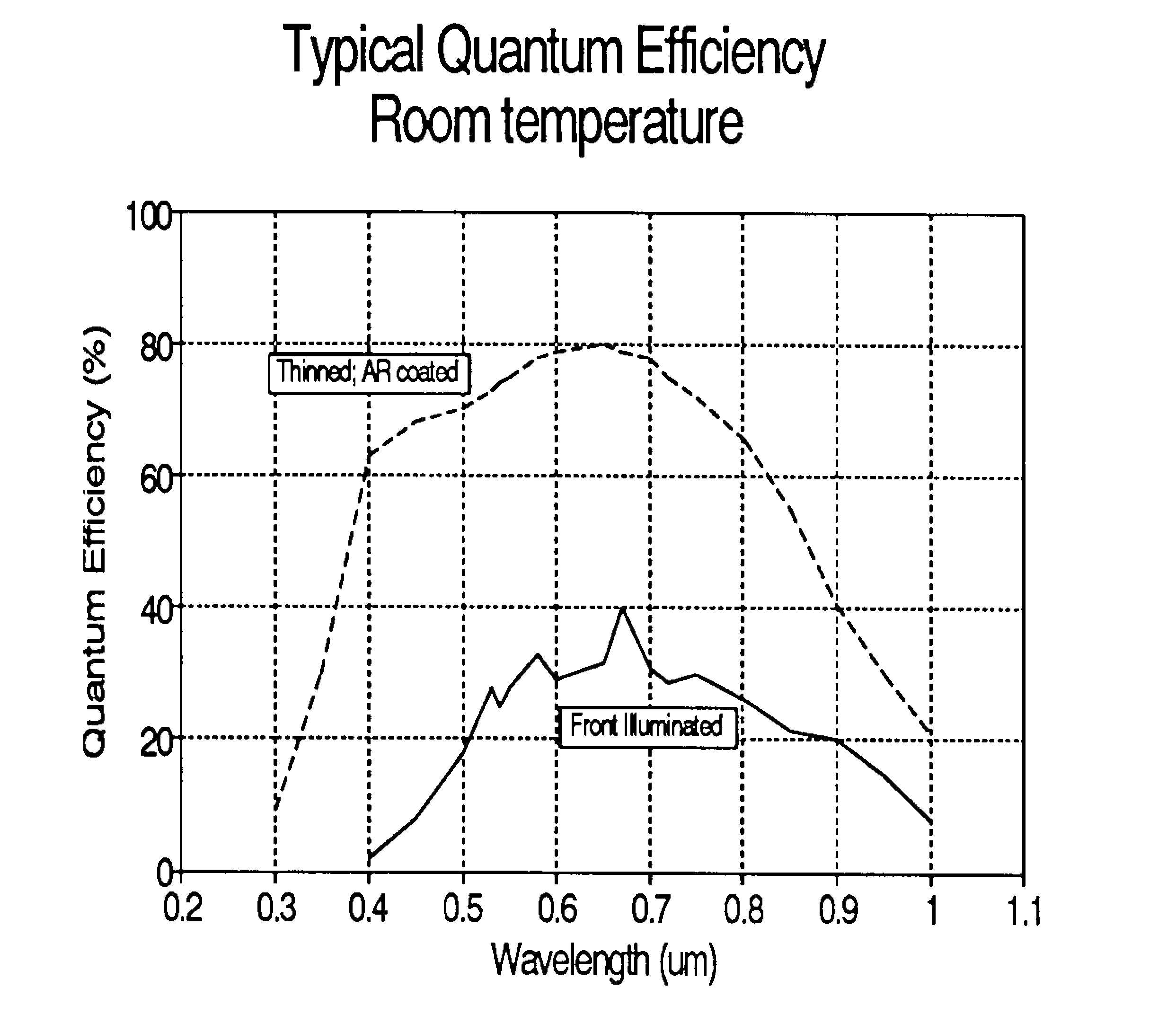

Hay algunas formas de hacer que un chip sea sensible al ultravioleta que las consideraremos en el punto que trata sobre la eficiencia cuántica, pero entre ellas se encuentra la utilización de CCD delgados, del orden de 10 a 20 micrones, e iluminados por detrás. Estos CCD delgados pueden llegar a hasta el 95% o más en su pico de sensibilidad. Los CCD delgados son los que más se están utilizando en estos momentos. En la figura 5-14 vemos las curvas para un chip adelgazado y grueso, mientras que en la figura 5-15 vemos la curva de sensibilidad para un chip Tektronix 1024 x 1024 pixeles en uso actualmente en CASLEO.

Figura 5.14: Comparación de la Eficiencia cuántica para un chip adelgazado y otro grueso.

Figura 5-15. Eficiencia cuántica para diferentes longitudes para el CCD TEK en uso en CASLEO.